Siemens Catapult High-Level Synthesis 2025

$ 170.00

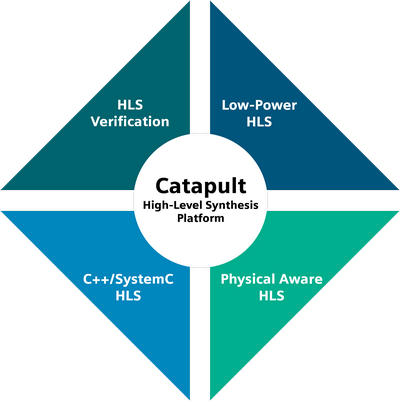

Boost your digital design productivity with Siemens Catapult High-Level Synthesis (HLS) 2025 — the industry-leading tool for converting C++ and SystemC designs into optimized RTL (VHDL/Verilog) code. Catapult 2025 accelerates ASIC and FPGA development, delivering higher performance, lower power, and faster verification. Ideal for AI, DSP, and SoC design engineers seeking advanced high-level synthesis automation and hardware-software co-design capabilities…

Description

Siemens Catapult High-Level Synthesis (HLS) 2025 – The Future of Algorithm-to-Hardware Design

Siemens Catapult High-Level Synthesis (HLS) 2025 represents the latest innovation in high-level synthesis automation, delivering unmatched performance, scalability, and accuracy for C++ and SystemC-based digital design. As part of the Siemens EDA portfolio, Catapult 2025 provides a unified and powerful environment that enables engineers to design, optimize, and verify hardware at a higher abstraction level—significantly reducing development cycles and improving time-to-market.

Catapult HLS bridges the gap between software algorithm development and hardware implementation, allowing engineers to describe system behavior in C++ or SystemC and automatically synthesize it into optimized RTL (Verilog or VHDL). The 2025 release introduces a series of groundbreaking features that make it the most advanced high-level synthesis solution on the market.

🚀 What’s New in Siemens Catapult HLS 2025

1. AI-Enhanced Synthesis Engine

The 2025 version introduces an AI-powered optimization engine capable of learning from design patterns and suggesting improved architectural implementations. This intelligent automation accelerates design space exploration and achieves the perfect balance between power, performance, and area (PPA)—cutting synthesis time by up to 40%.

2. Next-Generation RTL Generation

The new RTL engine delivers faster and more compact hardware structures, producing 25% smaller area utilization and higher clock speeds. With improved pipeline balancing, Catapult 2025 provides superior throughput for compute-intensive applications such as AI accelerators, image processing, and 5G communication systems.

3. Extended Language Support

Catapult HLS 2025 adds comprehensive support for C++20 and SystemC 2.3.4, enabling designers to leverage modern language constructs for greater expressiveness and maintainability. The enhanced compiler now supports lambda expressions, constexpr, and modular compilation, ensuring full compatibility with today’s advanced development workflows.

4. Seamless EDA Tool Integration

Integration with Siemens EDA’s Questa Advanced Verification, Calibre physical verification, and Aprisa place-and-route tools has been strengthened. This ensures a consistent and efficient end-to-end flow—from algorithm development and synthesis to verification and physical implementation.

5. Low-Power and Energy-Aware Design

With tighter integration of PowerPro technology, Catapult HLS 2025 automatically applies clock gating, power gating, and dynamic voltage scaling to reduce total power consumption without sacrificing performance. These new features are particularly valuable for mobile, IoT, and automotive applications.

6. Redesigned Graphical User Interface (GUI)

The updated GUI includes new interactive dashboards, enhanced visualization for performance metrics, and intuitive reports for area and timing analysis. Engineers can now compare multiple synthesis runs visually, simplifying architectural decision-making.

7. Improved Verification Flow

Catapult HLS 2025 introduces advanced SystemC-to-RTL co-simulation and enhanced formal equivalence checking, ensuring that every generated RTL block matches the high-level design specification accurately.

🌟 Key Highlights and Benefits

-

High-Level Productivity: Move from algorithm to hardware in days instead of weeks.

-

Multi-Domain Applications: Ideal for AI, DSP, SoC, automotive, networking, and 5G design.

-

Reduced Risk: Automatic synthesis minimizes human error and ensures consistent results.

-

Faster Design Space Exploration: Analyze hundreds of design alternatives with minimal manual intervention.

-

Scalable and Flexible: Supports both small academic designs and large enterprise-level SoC projects.

-

Future-Proof Technology: Ready for next-generation ASIC and FPGA processes.

🧩 System Requirements

Supported Operating Systems:

-

Windows 10 / Windows 11 (64-bit)

-

Linux (RHEL 8.x / 9.x, CentOS 8.x, Ubuntu 22.04 LTS or later)

Hardware Requirements:

-

CPU: Intel or AMD 64-bit multi-core processor (8+ cores recommended)

-

Memory: Minimum 32 GB RAM (64 GB or more recommended for complex SoCs)

-

Storage: 200 GB free disk space

-

GPU: OpenGL 2.0+ support for visualization tools

-

Network: Internet connection for license validation and updates

🛠️ Bug Fixes and Stability Improvements

The 2025 release delivers over 50 bug fixes and performance improvements across the synthesis, verification, and simulation workflows, including:

-

Resolved memory leak issues in large SystemC design compilation

-

Fixed synthesis errors related to nested template instantiations

-

Improved compatibility with Synopsys Design Compiler and Cadence Genus RTL outputs

-

Corrected clock-domain crossing (CDC) reporting inaccuracies

-

Enhanced multi-threading stability for large design simulations

-

Fixed UI responsiveness issues on high-DPI and 4K monitors

-

Improved report generation and synthesis progress tracking

⚡ Performance and Efficiency Gains

Benchmark testing shows that Siemens Catapult HLS 2025 delivers up to:

-

2× faster synthesis runtimes compared to previous versions

-

15–25% smaller RTL area footprint

-

Up to 20% lower power consumption on PowerPro-optimized designs

-

Improved verification convergence rates through tighter tool integration

🔐 Licensing and Availability

Catapult HLS 2025 is available through the Siemens EDA licensing portal with flexible node-locked and floating license options. Academic and enterprise licensing programs are also available for research institutions and design houses.

💡 Why Upgrade to Siemens Catapult HLS 2025

If you’re still using an older version of Catapult or a competing HLS tool, upgrading to Catapult 2025 provides tangible improvements in speed, efficiency, and synthesis quality. Whether you’re developing next-generation AI accelerators, automotive controllers, or FPGA prototypes, Catapult’s automation capabilities reduce complexity, enhance reliability, and bring designs to market faster.

⭐️⭐️⭐️⭐️⭐️ Excellent High-Level Synthesis Tool for Modern Hardware Design

As a senior digital design engineer working on ASIC and FPGA development, I’ve been using Siemens Catapult High-Level Synthesis (HLS) 2025 for several months, and it has truly transformed our workflow. The new version delivers impressive C++ and SystemC synthesis performance, producing optimized RTL that integrates seamlessly with our downstream Siemens EDA, Synopsys, and Cadence tools.

The AI-driven optimization engine and enhanced low-power design capabilities in Catapult HLS 2025 are game-changers. We’ve seen noticeable reductions in area utilization and power consumption, while achieving faster turnaround from algorithm to verified RTL. The improved GUI is also a huge plus—intuitive, responsive, and much easier to navigate than before.

What I appreciate most is the accuracy and reliability of the generated RTL. Even complex designs for AI accelerators and DSP pipelines compile cleanly with minimal manual tweaking. The tool’s integration with QuestaSim for co-simulation and Calibre for verification makes our entire EDA flow more efficient and consistent.

Overall, Siemens Catapult HLS 2025 is the best high-level synthesis software I’ve used to date. It’s fast, stable, and packed with practical innovations that boost productivity for serious hardware engineers. Highly recommended for anyone looking to accelerate ASIC and FPGA design with reliable C++ to RTL synthesis automation.

— Rajesh K., Senior FPGA Design Engineer