Synopsys IC Compiler II (ICC2) 2025.06

$ 150.00

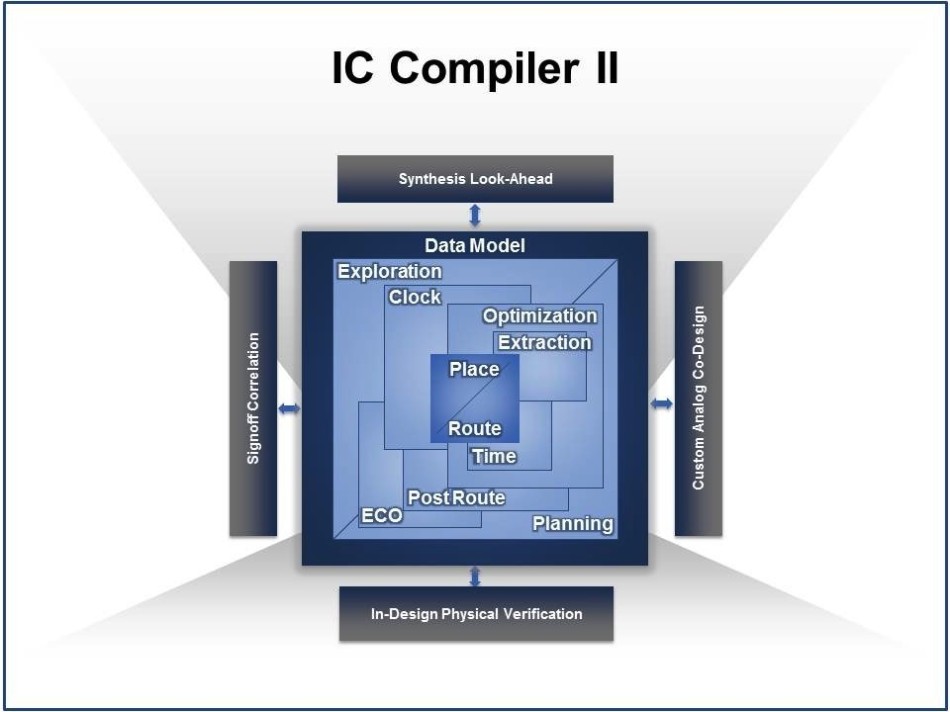

Synopsys IC Compiler II (ICC2) cutting-edge physical design and place-and-route technology for next-generation semiconductor design. Boost chip performance, reduce power, and accelerate time-to-market with this latest release…

Description

Synopsys IC Compiler II (ICC2) 2025.06 – Advanced Physical Design EDA Software

Synopsys IC Compiler II (ICC2) 2025.06 is the most powerful release yet of Synopsys’ industry-leading EDA (Electronic Design Automation) tool for physical implementation and place-and-route (P&R) design. This latest version continues to redefine what is possible in IC design, delivering new features, improved performance, and greater efficiency for complex semiconductor projects.

From 3nm and 2nm advanced process nodes to large-scale SoCs for AI, 5G, automotive, and data center applications, ICC2 2025.06 is built to meet the ever-increasing demands of today’s chip design challenges.

🔹 New Functions and Key Highlights

The 2025.06 release introduces major enhancements designed to accelerate design closure and optimize Power, Performance, and Area (PPA).

-

Advanced Node Readiness (3nm / 2nm):

Optimized algorithms for placement, routing, and timing closure at the most advanced technology nodes. -

Smarter Place-and-Route (P&R):

New distributed and multi-threaded processing boosts runtime speed by up to 30% faster compared to previous versions. -

AI-Driven Optimization:

Machine learning algorithms analyze timing, congestion, and power bottlenecks to deliver automated, smarter closure strategies. -

Power Reduction Engines:

Enhanced leakage and dynamic power optimization reduces total power consumption for low-power SoC designs. -

Congestion-Aware Routing:

Improved routing engines minimize congestion hotspots, ensuring clean DRC results and higher yield. -

Better GUI & Usability:

An updated modernized GUI, with faster rendering and customizable dashboards, improves design productivity for engineers. -

Seamless Fusion Compiler Integration:

Enhanced data sharing with Synopsys Fusion Compiler and PrimeTime signoff tools ensures accuracy and streamlined workflows.

🔹 System Requirements

To run Synopsys ICC2 2025.06 efficiently, the following system specifications are recommended:

-

Operating System: Linux RHEL 8.x / CentOS Stream 8 (64-bit preferred)

-

Processor (CPU): Intel Xeon or AMD EPYC, 8 cores minimum (16–32 cores recommended for large designs)

-

Memory (RAM): 32 GB minimum; 64 GB+ recommended for advanced-node or multi-million gate designs

-

Storage: 500 GB free disk space, SSD recommended for database-heavy operations

-

Graphics: X11-based Linux graphics system for GUI operation

-

Network: High-speed LAN or InfiniBand for distributed compute environments

By leveraging multi-core CPUs and large memory configurations, ICC2 2025.06 ensures fast and reliable physical design performance.

🔹 Bug Fixes and Stability Enhancements

This release focuses not only on new features but also on robust stability and reliability improvements:

-

Fixed memory leakage issues during large hierarchical routing operations.

-

Resolved timing convergence instability for hierarchical multi-block SoCs.

-

Enhanced runtime stability for designs exceeding 10 million instances.

-

Improved GUI responsiveness when loading complex designs with multiple layers.

-

Fixed integration bugs with PrimeTime and StarRC in signoff environments.

-

Patched multiple security vulnerabilities and implemented stronger license management protections.

-

Optimized runtime efficiency in both interactive and batch modes.

🔹 Why Choose Synopsys IC Compiler II (ICC2) 2025.06?

Synopsys IC Compiler II (ICC2) is trusted globally by semiconductor design leaders to achieve faster time-to-market, superior PPA, and higher yield. The 2025.06 release builds on this legacy, offering:

-

✅ Scalability for the Largest Designs – Handle billion-transistor SoCs with ease.

-

✅ Industry-Leading PPA Results – Deliver high-performance chips at lower power and area.

-

✅ Shorter Tapeout Cycles – Faster design closure saves weeks in the design cycle.

-

✅ Advanced Node Readiness – Fully optimized for 3nm, 2nm, and beyond.

-

✅ Seamless Tool Integration – Works smoothly with the Synopsys EDA ecosystem.

Whether you are developing 5G processors, AI accelerators, autonomous driving chips, or data center CPUs, ICC2 2025.06 provides the tools necessary to push silicon innovation further than ever before.

🔹 Applications of ICC2 2025.06

-

AI and Machine Learning SoCs – Achieve faster data throughput and power efficiency.

-

5G and Wireless Infrastructure – Optimize for high-frequency, low-latency designs.

-

Automotive Electronics – Deliver safety-critical, high-reliability semiconductor designs.

-

Cloud and Data Center Chips – Maximize performance for HPC and hyperscale computing.

-

Consumer Electronics – Build advanced processors for mobile, AR/VR, and IoT devices.

🔹 Conclusion

The release of Synopsys IC Compiler II (ICC2) 2025.06 marks a new milestone in EDA and IC design automation. By combining advanced algorithms, AI-driven optimization, powerful system integration, and unmatched stability, this version empowers design teams to deliver cutting-edge semiconductor solutions faster and with greater efficiency.

👉 Buy and download Synopsys IC Compiler II (ICC2) 2025.06 today to experience the next generation of physical implementation and place-and-route software.

⭐⭐⭐⭐⭐ Developer Review of Synopsys IC Compiler II (ICC2) 2025.06

As a semiconductor design engineer with over a decade of experience in EDA tools and physical implementation, I can confidently say that the Synopsys IC Compiler II (ICC2) 2025.06 release is a major step forward in chip design productivity.

The new AI-driven optimization features have noticeably improved timing closure and routing efficiency, especially on our large 5nm and 3nm SoC designs. Runtime is significantly faster compared to previous versions, and the multi-threading performance boost has saved our team many valuable hours during critical tapeout deadlines.

What I appreciate most about this release is the seamless integration with Fusion Compiler and PrimeTime. Data transfer between tools is smoother than ever, which helps avoid the bottlenecks we faced in older versions. The new power-aware placement and routing engines are also delivering measurable improvements in both leakage and dynamic power, which is crucial for our low-power mobile chip projects.

The updated GUI is cleaner and more responsive, making it easier for both new and experienced engineers to navigate complex designs. Stability has also been rock solid—no more unexpected crashes when handling multi-million instance designs, which was an issue in the past.

Overall, Synopsys IC Compiler II (ICC2) 2025.06 is not just an upgrade, but a real productivity accelerator for modern semiconductor design. If you are working on advanced process nodes, high-performance SoCs, or AI/5G applications, this tool is essential in your EDA toolkit.

⭐ Five stars – an outstanding release for physical design engineers.